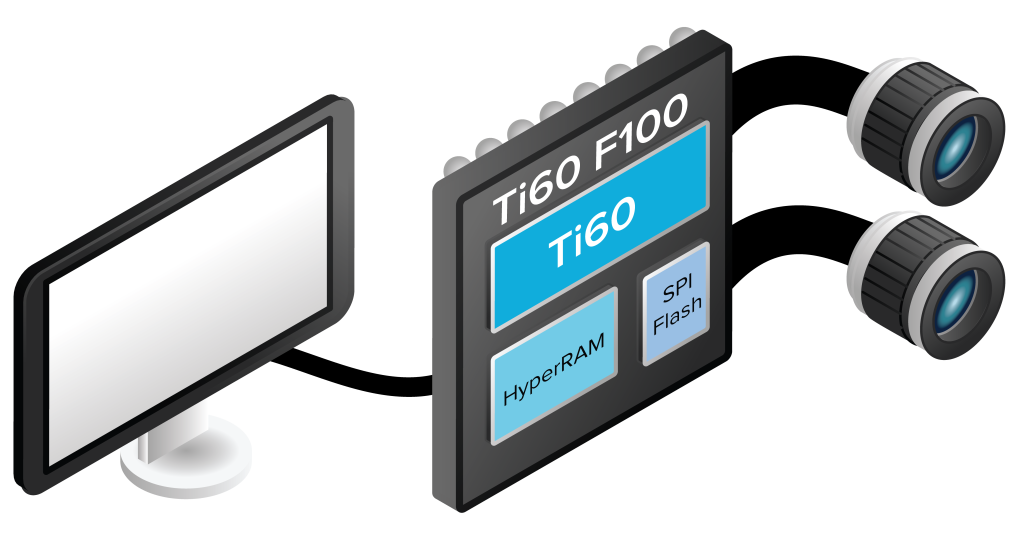

Diese Prozessor-Taktrate ist in vielen Fällen mehr als ausreichend, da die Datenverarbeitung mit höheren Performance-Ansprüchen parallel in der FPGA-Logik laufen kann. Das Prinzip ist am Efinix Edge-Vision-SoC und der Efinix TinyML-Platform zu sehen. Der Edge-Vision-SoC bindet anwenderspezifische Hardware-Beschleuniger per DMA an den RISC-V an und zeigt die Integration in das FPGA-Design sowie in das RISC-V-Programm. Die TinyML-Platform setzt auf Edge-Vision-SoC auf und beschleunigt verschiedene Lagen der neuronalen Netze, die als RISC-V-TinyML-Applikationen mit der TensorFlow Lite Micro C++ Library entwickelt werden.

Demo-Projekte und Loopback Design

Demo-Projekte ermöglichen zudem einen schnellen Einstieg in die Entwicklung. Dann folgt die Anpassung der Schnittstellen, der Peripherie und gegebenenfalls des RISC-V-Programms an die eigenen Anforderungen. Bevor die Software-Programmierung und damit die firmeneigene Produktspezifikation umgesetzt werden kann, wirft die Anpassung von MIPI-Parametern gelegentlich Fragen auf. Die Beispiele und Demos geben erste Antworten, wobei die Parameter natürlich auf die verwendeten Demo-Komponenten abgestimmt sind. Die Frage ist, wieweit die gewonnenen Erkenntnisse helfen, die eigene System-Spezifikation umzusetzen.

Vor oder parallel zur eigenen Baugruppenentwicklung, die zum Beispiel andere Bildsensoren verwenden wird, besteht die Möglichkeit MIPI-Schnittstellen mit der Zielkonfiguration zu testen. Falls der Sensor noch nicht zur Verfügung steht oder noch nicht an die Hardware angeschlossen werden kann, führt ein Weg über Loopback-Designs mit variabel einstellbaren Parametern. Anstelle des Sensors wird eine konfigurierbare Kombination aus MIPI-Transmitter mit Daten-Generator verwendet, die Daten über ein Loopback-Kabel an den ebenso konfigurierbaren MIPI-Receiver sendet. Zum Teil liegen entsprechende Kabel schon den Development Kits bei, darüber hinaus sind zusätzliche Adapter und Kabel leicht zu beschaffen.

Passende Loopback-Beispiele sind sowohl für MIPI CSI-2 als auch für MIPI DSI auf Anfrage erhältlich. Mit der Entwicklungssoftware Efinity und dem Development Kit bilden die Beispiele vorab ein Modell der Übertragungsstrecke, mit dem Parameter variiert und die Funktion im Logik-Debugger in Echtzeit überprüft werden. Wurden die Parameter beispielsweise eines Sensors oder eines Displays erfolgreich abgebildet und getestet, ist das Modell eine funktionale Referenz für das Zielsystem mit dem entsprechenden CSI-2-Sensor oder DSI-Display.

Ausblick

In Kürze wird ein Ti180-System-in-Package erhältlich sein, das aus einem FPGA mit 180k Logikelementen und einem LPDDR4 Memory besteht – ein SiP mit Abmessungen von 15x15mm, MIPI-DPHY, low Power, high Performance. Des weiteren sind Typen mit höherer Logik-Komplexität und weiteren schnellen Schnittstellen in Reichweite. Der Ti375 wird die Möglichkeiten der Titanium-Familie in Kürze um einen fest integrierten RISC-V und Highspeed Serdes, u.a. für PCI Express und Ethernet, ergänzen. Weiterhin mit dem Fokus auf geringe Verlustleistung und kleine Abmessungen.

www.efinixinc.com